| Technique                                     | Hit<br>Time | Band-<br>width | Mi<br>ss<br>pe<br>nal<br>ty | Miss<br>rate | HW cost/<br>complexity           | Comment                                                            |

|-----------------------------------------------|-------------|----------------|-----------------------------|--------------|----------------------------------|--------------------------------------------------------------------|

| Small and simple caches                       | +           |                |                             | -            | 0                                | Trivial; widely used                                               |

| Way-predicting caches                         | +           |                |                             |              | 1                                | Used in Pentium 4                                                  |

| Trace caches                                  | +           |                |                             |              | 3                                | Used in Pentium 4                                                  |

| Pipelined cache access                        | -           | +              |                             |              | 1                                | Widely used                                                        |

| Nonblocking caches                            |             | +              | +                           |              | 3                                | Widely used                                                        |

| Banked caches                                 |             | +              |                             |              | 1                                | Used in L2 of Opteron and<br>Niagara                               |

| Critical word first and early<br>restart      |             |                | +                           |              | 2                                | Widely used                                                        |

| Merging write buffer                          |             |                | +                           |              | 1                                | Widely used with write through                                     |

| Compiler techniques to reduce cache misses    |             |                |                             | +            | 0                                | Software is a challenge;<br>some computers have<br>compiler option |

| Hardware prefetching of instructions and data |             |                | +                           | +            | 2 instr., <mark>3</mark><br>data | Many prefetch instructions;<br>AMD Opteron prefetches<br>data      |

| Compiler-controlled<br>prefetching            |             |                | +                           | +            | 3                                | Needs nonblocking cache; in<br>many CPUs                           |

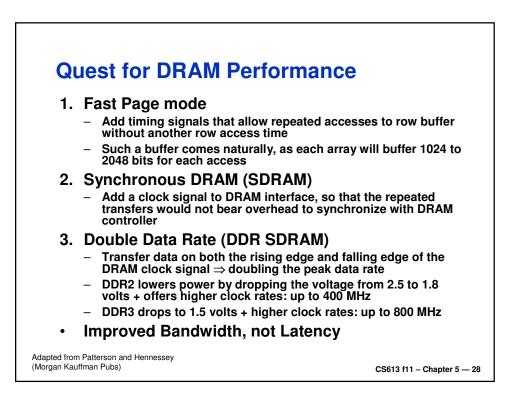

|        |                                                                                               |                     |                      | n Peak Chip<br>n Peak DIMN |                               |              |  |  |  |  |

|--------|-----------------------------------------------------------------------------------------------|---------------------|----------------------|----------------------------|-------------------------------|--------------|--|--|--|--|

|        | Stan-<br>dard                                                                                 | Clock Rate<br>(MHz) | M transfe<br>/ secor |                            | Mbytes/s/<br>DIM <del>M</del> | DIMM<br>Name |  |  |  |  |

| (B)    | DDR                                                                                           | 133                 | 266                  | DDR266                     | 2128                          | PC2100       |  |  |  |  |

| 25/    | DDR                                                                                           | 150                 | 300                  | DDR300                     | 2400                          | PC2400       |  |  |  |  |

| 6 (\$1 | DDR                                                                                           | 200                 | 400                  | DDR400                     | 3200                          | PC3200       |  |  |  |  |

| 94/06  | DDR2                                                                                          | 266                 | 533                  | DDR2-533                   | 4264                          | PC4300       |  |  |  |  |

| sale   | DDR2                                                                                          | 333                 | 667                  | DDR2-667                   | 5336                          | PC5300       |  |  |  |  |

| st for | DDR2                                                                                          | 400                 | 800                  | DDR2-800                   | 6400                          | PC6400       |  |  |  |  |

| ste    | DDR3                                                                                          | 533                 | 1066                 | DDR3-1066                  | 8528                          | PC8500       |  |  |  |  |

| Fa     | DDR3                                                                                          | 666                 | 1333                 | DDR3-1333                  | 10664                         | PC10700      |  |  |  |  |

|        | DDR3                                                                                          | 800                 | 1600                 | DDR3-1600                  | 12800                         | PC12800      |  |  |  |  |

|        | Adapted from Patterson and Hennessey X 8<br>(Morgan Kauffman Pubs) CS613 f11 - Chapter 5 - 29 |                     |                      |                            |                               |              |  |  |  |  |

- Focus here on protection

- 2 Other commercially important uses of VMs

- 1. Managing Software

- VMs provide an abstraction that can run the complete SW stack, even including old OSes like DOS

- Typical deployment: some VMs running legacy OSes, many running current stable OS release, few testing next OS release

- 2. Managing Hardware

- VMs allow separate SW stacks to run independently yet share HW, thereby consolidating number of servers

- Some run each application with compatible version of OS on separate computers, as separation helps dependability

CS613 f11 - Chapter 5 - 35

- Migrate running VM to a different computer

- » Either to balance load or to evacuate from failing HW

Adapted from Patterson and Hennessey (Morgan Kauffman Pubs)